# IN3027UG: Asynchronous Sample Rate Converter IP User Guide

The information disclosed to you hereunder (the "Materials") is provided solely for the selection and use of Intona products. To the maximum extent permitted by applicable law: (1) Materials are made available "AS IS" and with all faults, Intona hereby DISCLAIMS ALL WARRANTIES AND CONDITIONS, EXPRESS, IMPLIED, OR STATUTORY, INCLUDING BUT NOT LIMITED TO WARRANTIES OF MERCHANTABILITY, NON-INFRINGEMENT, OR FITNESS FOR ANY PARTICULAR PURPOSE; and (2) Intona shall not be liable (whether in contract or tort, including negligence, or under any other theory of liability) for any loss or damage of any kind or nature related to, arising under, or in connection with, the Materials (including your use of the Materials), including for any direct, indirect, special, incidental, or consequential loss or damage (including loss of data, profits, goodwill, or any type of loss or damage suffered as a result of any action brought by a third party) even if such damage or loss was reasonably foreseeable or Intona had been advised of the possibility of the same. Intona assumes no obligation to correct any errors contained in the Materials or to notify you of updates to the Materials without prior written consent. Intona products are not designed or intended to be fail-safe or for use in any application requiring fail-safe performance.

© Copyright Intona Technology GmbH, Germany.

Intona and other designated brands included herein are trademarks of Intona in Germany and other countries. All other trademarks are the property of their respective owners.

Website: https://intona.eu

### Contents

| 1 | 1.1       Features                                                                                                                                                           | 3<br>3<br>3<br>3<br>3 |

|---|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| 2 | Application                                                                                                                                                                  | 3<br>4<br>4           |

| 3 |                                                                                                                                                                              | 4                     |

| 0 | 3.1    Asynchronous Mode      3.2    Synchronous Mode                                                                                                                        | 5<br>5                |

|   | 3.4 Health Module                                                                                                                                                            | 6<br>6                |

|   | 3.6 Quad Mode                                                                                                                                                                | 6<br>6<br>6           |

|   | 3.6.2 Upsampling to 192 kHz                                                                                                                                                  | 7<br>7                |

|   | 3.8.1 Common Signals and Parameters                                                                                                                                          | 7<br>7<br>8           |

|   |                                                                                                                                                                              | 9                     |

|   | 3.8.5 Massive Parallel                                                                                                                                                       |                       |

| 4 | Simulation       1         4.1 Prerequisites to run the Simulation       1         4.2 Running a Simulation       1         4.2.1 Example: asrc_system_parallel_32ch       1 | 2<br>2                |

| 5 | Performance         1           5.1         THD+N         1                                                                                                                  |                       |

|   | 5.2Frequency Response15.3Group Delay1                                                                                                                                        |                       |

| 6 | Resource Utilization16.1 Device vs. Maximum Channel Count1                                                                                                                   | 5                     |

| _ | 6.2 Channel Count vs. Occupied Slices                                                                                                                                        |                       |

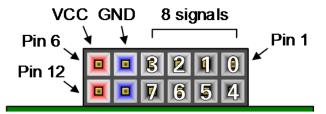

| 7 | Evaluation of the Core using Digilent Arty       1         7.1       Connecting the Core                                                                                     | 6                     |

|   | 7.1.1       Arty Filou Filou Filou       1         7.1.2       FPGA Pinout Map       1         7.1.3       Actual Connections       1         7.1.4       Switches       1   | 6<br>6                |

|   | 7.1.5Status Indicators17.1.6Signal Constraints1                                                                                                                              | 7<br>7                |

| _ | 7.2 Binaries                                                                                                                                                                 |                       |

| 8 | Appendix       1         8.1       Definition of Speed Modes       1                                                                                                         |                       |

### 1 Introduction

The Intona Asynchronous Sample Rate Converter solution comprises rate conversion to any number of uncompressed PCM audio channels as Intellectual Property (IP) core. The design is FPGA-verified and provided in human-readable Verilog-HDL. The solution excels in low latency and low logic resource allocation at professional grade audio quality.

### 1.1 Features

The design consists of a polyphase FIR filter that feeds the subsequent convolution process, where the actual resampling happens, with the desired intermediate values. The polyphase is selected out of 4096 predefined coefficients using cubic interpolation with 28 bits of decimal precision. Effective applied taps are in the range of 8 to 66, depending on ratio and output samplerate. A latency counter is provided within the simulation. Because of the uniform FIFO and interpolator interface, there is no conceptual restriction in channel count.

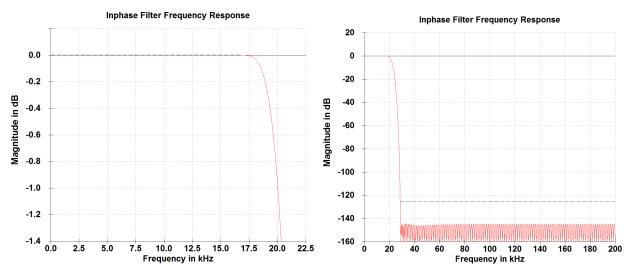

Any arbitrary, synchronous or asynchronous upsampling or downsampling of 24 bit data in the range of 30 to 230 kHz is supported. The resulting THD+N within the audio band is typically better than -135 dB. The channel count is always static and gets not reduced in double or quad mode. A high precision ratio detector for asynchronous deployment is included.

The core is fully pipelined and designed to be as economical as possible regarding logic, RAM and multiplier use. Resource usage can be further optimized by using a fixed system sample rate and by omitting the quad speed mode.

### 1.2 Requirements

Any FPGA that is capable to run the core logic at desired clock frequency.

Although this core does not require dedicated hardware building blocks such as multipliers or RAMs, it is strongly recommended to make use of pipelined multipliers to achieve optimum speed vs. area.

For the simulation, Verilator and a C++ compiler on macOS or Linux is required. WAV files or VCD logic files can be generated for inspection and verification.

### 1.2.1 Native Multipliers

The core uses 32x32-to-36 bit multipliers as defined in **asrc\_mult32.v**. This original Verilog version is primarily used for simulation. In hardware, it is recommended to use one of the pre-generated cores. Provided are cores for Spartan 6 and 7-series (all models). For other FPGA models, the designer may generate those by using the FPGA vendor tools.

Usually, the coefficient core will utilize 4xMULT18/DSP48. The convolution kernel uses 4xMULT18/DSP48 per 32 channels.

### 1.2.2 RAM buffers

The coefficient data ROM and the FIFO buffers are described in pure Verilog-HDL and will be instantiated automatically as dedicated RAM blocks by the synthesizing process.

### 1.3 Licensing and Ordering

This IP core solution is provided under the terms of the Intona IP Core License Agreement. For full access to all HDL sources for core functionalities in simulation and in hardware you must purchase a

license for the core. Evaluation licenses are available in form of binary modules with hardware timeout. Contact Intona f or information about pricing and availability.

Ordering code of this core is IN8083IP.

## 2 Application

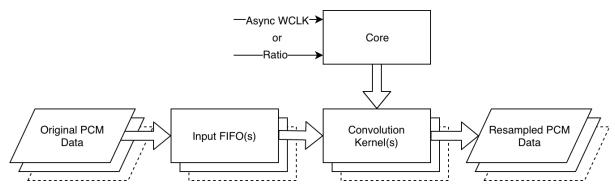

In a typical application, the sample rate converter consists of three parts.

One or more Input FIFO(s) that can hold enough samples for the convolution. Any number of input FIFOs may be connected to one core. Multiple variations are provided and can be used arbitrarily.

(a) asrc\_fifo\_parallel accepts pipelined parallel PCM input

(b) **asrc\_fifo\_tdm\_4x8** accepts serial TDM data with four strides, up to eight channels each An input FIFO is basically a dual ported RAM. The designer is free to connect their own design in place of the provided ones.

- 2. The core itself (**asrc\_core**), which computes the right tap value for the convolution at the right time. The core also determines the ratio between input and output when set to asynchronous mode. One core is needed per direction. One core serves any amount of I/O channels.

- 3. One or more convolution kernels (asrc\_convolute). Each convolution kernel applies the actual resampling to the PCM data held in the respective input FIFO for up to 32 channels. The output is always random access parallel PCM and may be double buffered. Several examples are provided for converting the results to TDM or massive-parallel data.

For bidirectional resampling, the dedicated core **asrc\_core\_bidir** is provided. This actually instantiates two cores that share one set of coefficients as dual-ported ROM. In contrast to using two unidirectional cores in parallel, this saves LUT resources, and 8 to 12 kBytes of block RAM.

### 2.1 Block Diagram

### 3 Designing with the Core

It is recommended to use the sources directly by copying or sym-linking the contents of the rtl directory to your FPGA hdl sources directory. The provided examples demonstrate how to use the core with a variety of application scenarios.

If you prefer using pre-synthesized netlists, there are some helper scripts provided (ISE only). You need to select a target in the target.cfg file and run ./make\_netlist.sh in the top directory of the package. A ngc file will be generated.

#### 3.1 Asynchronous Mode

If the parameter MANUAL\_RATIO is set to 0, the ratio between input and output word clocks is determined by the core. The internal moving average detector measures the time between two word clock events at 26 bits precision. The time constant is about one second. It also calculates the reciprocal that is needed to scale the output amplitude during downsampling. The direction signal reverses the average value with the reciprocal, hence allowing resampling to upstream.

| direction | Description                                             |

|-----------|---------------------------------------------------------|

| 1'b0      | Resample arbitrary incoming audio to the internal clock |

| 1'b1      | Resample internal audio to the foreign clock            |

Connect the source of the foreign word clock to the async\_wclk input.

**Clock Domain Crossing** Asynchronous inputs need special attention. To avoid metastability, you should always re-register them to the local high speed clock with a pipeline of at least two registers.

The asrc\_core features the 8-bit output iodiv\_out[7:0], which is a copy of iodiv\_r[30:23]. You may use this as an indicator in your application if you need to know at which ratio the resampler is currently working.

#### 3.2 Synchronous Mode

If parameter MANUAL\_RATIO is set to 1, the core does not derive the ratio from the input word clock. A valid ratio and its reciprocal must be given in 4.28 fixed point format to iodiv\_manual and iodiv\_r\_manual. They may be changed arbitrarily at runtime without resetting the core.

async\_wclk (the input pin for asynchronous word clock) is ignored in synchronous mode. The core just eats up the samples that are fed into the internal FIFO by triggering new\_frame synchronously. Just like in asynchronous mode, there is no requirement on phase relationship between input and output word clock (other than being synchronous to the high frequency core clock).

iodiv\_manual must represent the 4Q28 fixed point value of Fs<sub>in</sub> divided by Fs<sub>out</sub> and iodiv\_r\_manual, its reciprocal.

| Speed Mode In | Speed Mode Out | out_speedmode[1:0] | iodiv_manual[31:0] | iodiv_r_manual[31:0] |

|---------------|----------------|--------------------|--------------------|----------------------|

| Single        | Single         | 2'd0               | 32'h1000_0000      | 32'h1000_0000        |

| Single        | Double         | 2'd1               | 32'h0800_0000      | 32'h2000_0000        |

| Single        | Quad           | 2'd2               | 32'h0400_0000      | 32'h4000_0000        |

| Double        | Single         | 2'd0               | 32'h2000_0000      | 32'h0800_0000        |

| Double        | Double         | 2'd1               | 32'h1000_0000      | 32'h1000_0000        |

| Double        | Quad           | 2'd2               | 32'h0800_0000      | 32'h2000_0000        |

| Quad          | Single         | 2'd0               | 32'h4000_0000      | 32'h0400_0000        |

| Quad          | Double         | 2'd1               | 32'h2000_0000      | 32'h0800_0000        |

| Quad          | Quad           | 2'd2               | 32'h1000_0000      | 32'h1000_0000        |

### 3.3 Reset Signal

The core is partly reset at active high of the reset input signal. You may tie this to your internal reset logic. This pin is optional. Tie to **1'b0** if not used.

In general, there is no lockup situation known to that the core would need a reset. If it gets wrong signals, it will output wrong values. If the fed signals become valid again, the core will resume with valid output. Use the **asrc\_health** module to mute or re-route your outputs if invalid signals are unacceptable.

### 3.4 Health Module

The **asrc\_health** module checks some states and the "good" output goes high if the internal FIFOs are not full or empty. It can be used to enable other circuity in the design, such as mute events.

### 3.5 Core Clock

The core is designed and tested to be clocked at 122.288 MHz for 48/96/192k or at 112.896 MHz for 44.1/88.2/176.4k sample rates. It expects the local frame sync to happen every **fclk / fsamplerate**, which depends on the sample speed mode, as shown in the following table:

| Sample Speed | Core Clock Ticks per Output Frame |

|--------------|-----------------------------------|

| Single       | 2560                              |

| Double       | 1280                              |

| Quad         | 640                               |

The core triggers at rising edge of the target frame sync signal (**out\_framesync**).

In synchronous mode (MANUAL\_RATIO=1) any other core clock can be accepted by the core, as long the "ticks per output frame", as stated in the table above value, is attainable. For example if your system is clocked at 130 MHz, this will work perfectly fine.

### 3.6 Quad Mode

This core is designed to accept quad speed sample rates when the parameter **QUAD\_AVAIL** is set to 1. Setting it to 0 will save 4096 bytes of occupied RAM and the highest acceptable samplerate will drop to about 113 kHz.

There is no hysteresis in changing internal modes when changing sample rate arbitrarily. Notably the edges between double and quad modes should be avoided. It is recommended to use the core within following sample rates:

Usable ranges are:

Fs<sub>in</sub> 30..113kHz and 115..230kHz.

The ratio between input and output samplerate must not be larger than 4.999.

### 3.6.1 Downsampling from 192 kHz

Downsampling from e.g. 192kHz to 48kHz is challenging because it would require 128 taps per  $Fs_{out}$  which is beyond the maximum of possible taps in this design. It is common to skip the first half of the coefficients this case, effectively scaling it down to 64 taps. However, just skipping does not deliver enough amount of alias image rejection and this is not satisfying the standards of professional audio

equipment. Hence, there is a second coefficient set available which is was optimized to 64 taps at quad downsampling rates.

### 3.6.2 Upsampling to 192 kHz

The maximum number of possible taps shrink down because the core algorithm needs 32 clock cycles to fetch and interpolate a polyphase tap. At 192 kHz, this would require a core clock of 245.76 MHz. Because this clock is not possible with today's budget FPGAs, this mode is implemented to use the second coefficient set that is available in half of the original size.

### 3.7 Determining Latency

The simulation has a single-shot peak detector implemented. The Fs time of the first positive peak of each input and output will be saved in a variable and the result is printed to the console when the simulation is done. This could also be implemented as zero-crossing detector but that technique suffers from false-positives when possible pre-ringing occurs, so peak detection is preferred.

Simulation done.

Measured latency: 10 fs\_out samples

### 3.8 Provided Application Examples

3.8.1 Common Signals and Parameters

parameter QUAD\_AVAIL

See Quad Mode.

parameter MANUAL\_RATIO

See Synchronous Mode and Asynchronous Mode.

For other individual signals, see the source files for further explanation of the individual ports.

### 3.8.2 Parallel pipelined Input and RAM-interfaced Output

Parallel input words are fed into the resampler at rising edge of **new\_word**. After 2<sup>CH\_BITS</sup> words have been fed, a **new\_frame** pulse must follow to mark the end of frame.

The double buffered output can be read through the RAM interface with **d\_out\_ch** as address and **d\_out** as data.

```

module asrc_system_parallel_ramif

#(

parameter

CH_BITS

= 5,

QUAD_AVAIL

= 1,

parameter

MANUAL_RATIO = 0

parameter

)

(

input

clk,

input

reset,

input

out_framesync,

[1:0]

input

out_speedmode,

input

direction,

input

async_wclk,

[31:0] iodiv_manual,

input

input

[31:0] iodiv_r_manual,

new_word,

input

input

new_frame,

input

[23:0] d_in,

input

[CH_BITS-1:0]

d_out_ch,

[23:0] d_out,

output

output

good

);

```

### 3.8.3 TDM, Unidirectional

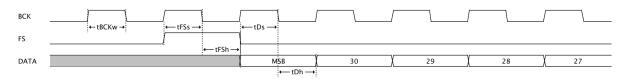

Four lanes of eight channels, MSB first, with one-early frame sync. Also available as **asrc\_system\_tdm\_4x2**, which handles four lanes of two channels.

```

module asrc_system_tdm_4x8

#(

QUAD_AVAIL

= 1,

parameter

parameter

MANUAL_RATIO = 1

)

(

input

clk,

input

reset,

input

[1:0]

out_speedmode,

good,

output

[31:0] iodiv_manual,

input

[31:0] iodiv_r_manual,

input

direction,

input

input

async_wclk_in,

input

tdm_in_bck,

input

tdm_in_fs,

input

[3:0]

tdm_in_d,

input

tdm_out_bck,

input

tdm_out_fs,

output [3:0]

tdm_out_d

);

```

Maximum BCK frequency for the TDM modules is 24.576 MHz.

#### 3.8.4 TDM, Bidirectional

Same as unidirectional, but duplicated ports for additional resampling to upstream direction. This makes use of the bidirectional **asrc\_core\_bidir**, which will share the coefficient ROM between the two resamplers.

```

module asrc_system_tdm_4x8_bidir

#(

QUAD_AVAIL

parameter

= 1,

MANUAL_RATIO = 1

parameter

)

(

input

clk,

input

reset,

input

[1:0]

out_speedmode,

output

good,

[31:0] iodiv_manual,

input

input

[31:0] iodiv_r_manual,

input

direction,

input

async_wclk_in,

input

tdm_in_bck,

input

tdm_in_fs,

input

[3:0]

tdm_in_d,

input

tdm_out_bck,

input

tdm_out_fs,

output [3:0]

tdm_out_d,

// second resampler, other direction:

input

[1:0]

out_speedmode_1,

input

tdm_in_bck_1,

input

tdm_in_fs_1,

[3:0]

input

tdm_in_d_1,

tdm_out_bck_1,

input

input

tdm_out_fs_1,

output [3:0]

tdm_out_d_1,

output

good_1

);

```

#### 3.8.5 Massive Parallel

No less than 32 parallel inputs and outputs.

```

module asrc_system_parallel_32ch

#(

QUAD_AVAIL

parameter

= 1,

MANUAL_RATIO = 1

parameter

)

(

input

clk,

input

reset,

input

[1:0]

out_speedmode,

output

good,

[31:0]

iodiv_manual,

input

input

[31:0]

iodiv_r_manual,

input

async_wclk_in,

input

direction,

wclk_in,

input

input

[23:0] pcm_in_1,

input

[23:0] pcm_in_2,

input

[23:0] pcm_in_3,

. . .

input

[23:0] pcm_in_31,

[23:0] pcm_in_32,

input

input

wclk_out,

output reg [23:0] pcm_out_1,

output reg [23:0] pcm_out_2,

output reg [23:0] pcm_out_3,

. . .

output reg [23:0] pcm_out_31,

output reg [23:0] pcm_out_32

);

```

### 4 Simulation

Simulation is done using the high performance open source Verilog simulator Verilator, which effectively converts Verilog to C++. The output compiles to a native binary, which can be run on a PC.

Simulation presumes a Linux (or other Unix, e.g. Mac) command line terminal. On Windows, this may work using WSL (Windows Subsystem for Linux).

### 4.1 Prerequisites to run the Simulation

Find dependencies and installation instructions of the Verilator simulation suite on this web site<sup>1</sup>. It is recommended to build from Git.

On Debian-flavoured systems, the installation of Verilator including dependencies is simple:

sudo apt-get install verilator

### 4.2 Running a Simulation

The system top module, written in C++, generates a stimulus. This is one of static sine tone, swept sine tone or Dirac impulse and it outputs a mono WAV file with the simulated result. Static sine tone is used for THD+N calculation. Swept sine can be used to show aliasing images using sndfile-spectrogram (which is part of libsndfile sndfile-tools<sup>2</sup>). The Dirac stimulus will create an impulse response that can be used to inspect the frequency response by using deconvolution.

Verilator uses a much faster simulation technique than classical simulators, such as Icarus Verilog. You can expect to simulate five seconds of signal in ten to thirty seconds on a decent machine. Classic simulators would need several hours or even days for the same task.

For signal inspection using GTK Wave or the like, Verilator can output simulation data in VCD file format. You need to set **WRITE\_TRACE** to 1 at the top of the corresponding C++ file.

| т                                                           | Signals                           | Waves                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 245850 us                               |                               | 245860 us |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-------------------------------------------------------------|-----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|-------------------------------|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TOP                                                         | Time<br>clk=1                     | and the second se |                                         |                               | 215000 45 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| asrc_system                                                 |                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                         |                               |           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| asrc_avrg                                                   | sys_framesync=0                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                         |                               |           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| → asrc_convolute                                            | good =1<br>new frame =0           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                         |                               |           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                                             |                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                         |                               |           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| asrc_mult32                                                 | new_tap =0                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                         |                               |           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| - asrc_fifo_parallel                                        | new_word =0                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                         |                               |           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| asrc_health     asrc_outbuf_parallel                        | taps_done =0                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                         |                               |           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| <ul> <li>asrc_outbur_parallel</li> <li>asrc_proc</li> </ul> | accu_new =1                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                         | AND COMMENTATION AND COMMENTS |           | and the second the second the second the second the second s |

| asrc_mult32                                                 | p[35:0] =0005A1DBD                | 00000000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 000000000000000000000000000000000000000 | 000000000                     | 000000000 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| asrc_rom                                                    | sync_fs =0                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                         |                               |           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| p in genblk1                                                | accu_ch[4:0] =01                  | 00 00                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 00                                      | 00                            | 00        | k                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| P 112 generici                                              | d_out_ch[4:0] =1F                 | 1F                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 1F                                      | 1F                            | 1F        | 1F                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                                                             | accu_bufsel =1                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                         |                               |           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                                             | last_sync_fs =0                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                         |                               |           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Signals                                                     | microcode_a[4:0] =10              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                         |                               |           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| BF[31:0]                                                    | loop =0                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                         |                               |           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| BI[31:0]                                                    | <pre>i microcode_a[4:0] =10</pre> | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                         |                               |           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| CONST_1[31:0]                                               | good =1                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                         |                               |           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |